AAAS Intelligent Computing Volume 2022, Article ID 9806758, 32 pages https://doi.org/10.34133/2022/9806758

# Review Article

# **Software Systems Implementation and Domain-Specific Architectures towards Graph Analytics**

Hai Jin, Hao Qi, Jin Zhao, Ainyu Jiang, Yu Huang, Chuangyi Gui, Qinggang Wang, Xinyang Shen, Yi Zhang, Ao Hu, Dan Chen, Chaoqiang Liu, Haifeng Liu, Haiheng He, Xiangyu Ye, Runze Wang, Jingrui Yuan, Pengcheng Yao, Yu Zhang, Long Zheng, and Xiaofei Liao

Correspondence should be addressed to Yu Zhang; zhyu@hust.edu.cn

Received 18 August 2022; Accepted 10 October 2022; Published 29 October 2022

Copyright © 2022 Hai Jin et al. Exclusive Licensee Zhejiang Lab, China. Distributed under a Creative Commons Attribution License (CC BY 4.0).

Graph analytics, which mainly includes graph processing, graph mining, and graph learning, has become increasingly important in several domains, including social network analysis, bioinformatics, and machine learning. However, graph analytics applications suffer from poor locality, limited bandwidth, and low parallelism owing to the irregular sparse structure, explosive growth, and dependencies of graph data. To address those challenges, several programming models, execution modes, and messaging strategies are proposed to improve the utilization of traditional hardware and performance. In recent years, novel computing and memory devices have emerged, e.g., HMCs, HBM, and ReRAM, providing massive bandwidth and parallelism resources, making it possible to address bottlenecks in graph applications. To facilitate understanding of the graph analytics domain, our study summarizes and categorizes current software systems implementation and domain-specific architectures. Finally, we discuss the future challenges of graph analytics.

### 1. Introduction

The amount of graph data that represents relationships is rapidly expanding as a result of the widespread popularization of the Internet, the emergence of the Internet+, the digital transformation of society, and the fast growth of the economy [1]. For example, Facebook's social network contains more than 1.71 billion graph vertices and 100 billion graph edges, according to the most recent statistics it provided in December 2016. The need for connected data analysis is rising at the same time, leading to an increase in the volume of graph-structured data in many significant application sectors, including financial analysis, power system operation, social life, and national security monitoring. To effectively analyze and derive relevant information from this graph data, graph computing technology is quickly being developed. Applications for graph computing are increasingly moving away from traditional binary scenarios and into a variety of kinds, structures, and attributes [2, 3]. Complex graph applications, such as graph mining and graph learning, are continuously developing in addition to traditional graph applications (such as graph processing). In this paper, each of these names (graph processing, graph mining, and graph learning) refers only to a specific class of applications as follows:

Graph Processing. Conventional graph algorithms (such as the PageRank for ranking, the adsorption for video recommendation, the single-source shortest path (SSSP) for road selection, and the connected component for clustering) are designed to process graphs iteratively until convergence. Many operations of such graph algorithms are based on traversal operations and generally focus on performing linear algebra-like computational operations on the graph. Compared with traditional computing models, iterative graph algorithms have rich, efficient, and agile analysis capabilities for relational data, and are widely used in real life. For

<sup>&</sup>lt;sup>1</sup>National Engineering Research Center for Big Data Technology and System, Services Computing Technology and System Lab, Cluster and Grid Computing Lab, School of Computer Science and Technology, Huazhong University of Science and Technology, Wuhan, China

<sup>&</sup>lt;sup>2</sup>Zhejiang-HUST Joint Research Center for Graph Processing, Zhejiang Lab, Zhejiang, China

example, Google needs to regularly rank the influence of hundreds of millions of web pages on the web, and Facebook needs to iteratively analyze its social network graph to control the structural state of the social network and improve the accuracy of advertising delivery

Graph Mining. Graph mining (such as clique finding (CF), motif counting (MC), and frequent subgraph mining (FSM) aims to discover specific structures or patterns in graphs. In addition to the properties of traditional data mining techniques, graph mining technology is an ideal tool for dealing with complex data structures because of its complex data object relationships and rich data presentation. Knowledge and information acquisition through graph mining has been widely used in various fields, such as social sciences [4, 5], bioinformatics [6, 7], and cheminformatics [8, 9]. Specifically, graph mining can be used to discover structurecontent relationships in social media data, to mine community-dense subgraphs, to extract network motifs or significant subgraphs in protein-protein or gene interaction networks, to discover 3D motifs in protein structures or chemical compounds, etc.

Graph Learning. As a typical representative of non-Euclidean spatial data, graphs can characterize the relationships between everything. However, due to the irregularity of graph data, existing deep learning models [10] (which deal with Euclidean Space [11] data and are based on the nature of regularized data) cannot be directly applied to graph structured data. For this reason, graph learning (such as graph neural network (GNN) [12] and graph embedding [13]) was developed. Graph neural networks establish a deep learning framework for non-Euclidean spatial data, and compared to traditional network representation learning, it is able to perform deeper information aggregation operations on graph structures than traditional network representation learning models. Currently, graph neural networks are capable of solving many deep learning tasks, link prediction [14], graph clustering [15], and recommendation systems [16]

The fact that these three classes of graph applications are so widely used motivates us to investigate them. Due to the characteristics of sparsity, power-law distribution, and small-world structure of the graph, graph computing brings a series of challenges to modern computer systems based on control flow architecture, such as low execution efficiency of parallel flow, low locality of memory access, and poor scalability of lock synchronization. Therefore, graph computing has recently been a popular topic for study in both academia and industry.

In order to solve many problems of large-scale graph computing, in recent years, researchers have carried out extensive basic research and key technology research on software systems implementation, which mainly focuses on improvements by software technologies on existing general-purpose hardware platforms, such as single-machine platform and distributed platform. However, there is a significant gap between the general-purpose hardware and the unique characteristics of graph analytics [17, 18]. Domain-specific architectures, which primarily pay attention to hardware acceleration through architecture innova-

tions, are necessary as a potential solution that may fill the gap. We classify the domain-specific architectures' research into three major categories, FPGA, ASIC, and PIM, because different hardware platforms have different considerations for performance acceleration.

This paper will summarize the research status of graph computing key technologies of the software systems implementation and domain-specific architectures, and then summarize, compare, and analyze the latest research progress from three aspects: basic theory, system software, and system architecture. The remainder of this paper is structured as follows: Section 2 explains the background of graph terminology and graph accelerator architecture types. Section 3 describes software systems implementation for graph analytics. Section 4 presents domain-specific architectures for graph analytics. Finally, Section 5 prospects the future technical challenges and research directions, and Section 6 provides a conclusion.

### 2. Background

2.1. Graph Terminology. A graph is a kind of data structure made up of vertices and the edges that connect vertices. The formula for a graph is G = (V; E), where V stands for the vertex set and E for the edge set. A directed edge from vertex  $v_i$  to vertex  $v_j$  is represented as  $e = (v_i; v_j)$ . Each vertex and each edge has its attribute value at the same time. Different domain attribute values can represent different meanings. For instance, in a social network, the attribute value of the vertex is the popularity of the individual, and the attribute value of the edge is expressed as the degree of closeness between two people who are related. The graph data structure expresses the correlation between data well, and correlation computing is the foundation of big data computing. By obtaining the correlation of data, useful information can be extracted from the massive data with a lot of noise. Graph analytics technology solves the problems of low efficiency and high cost of association queries in traditional computing modes and fully characterizes the relationship in the problem domain, and has rich, efficient, and agile data analysis capabilities.

2.2. Domain-Specific Architecture Types for Graph Analytics. FPGA-Based Architecture. Field-programmable gate arrays (FPGAs) are integrated circuits that consist of various types of programmable resources, which enables developers to rapidly prototype application-specific accelerators using dedicated hardware description languages and reconfigure these accelerators as often as needed. These programmable resources include but not limited to lookup tables (LUTs), registers, block RAMs (BRAMs), and DSP slices. However, FPGAs offer reconfigurability at the expense of lowered clock frequencies, which is about  $10 \times 100$  lower than that of CPUs. Nevertheless, FPGAs have become attractive devices for accelerating graph applications due to the following advantages.

First, graph-application-specific operations can be elaborately constructed as a pipeline to yield one result per cycle, expressing impressive efficiency. Meanwhile, the pipeline

duplication can be easily implemented on the FPGA, enabling massively parallel graph processing. Furthermore, graph data can be streamed into the pipeline and trigger the computation instead of expensive instruction control operations (e.g., instruction decoding) in modern CPUs and GPUs, reducing power consumption significantly. The random access feature of on-chip BRAMs is another representative advantage of FPGAs, which enables random graph data access with high throughput on FPGAs. What is more, developers can explicitly configure the on-chip BRAMs with the domain-specialized replacement policy, which is fundamentally different from the domain-agnostic cache replacement strategy on CPUs, thereby exploiting locality and reducing off-chip communications effectively. Nowadays, FPGAs have been widely deployed in the cloud or data centers such as Microsoft Project Catapult [19] and Amazon F1 cloud [20]. The accessibility and low cost of FPGAs further make them attractive.

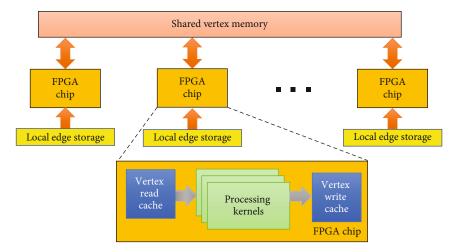

The aforementioned advantages of FPGAs have attracted a good deal of research in developing FPGA-based specialized architecture for accelerating graph application. To mitigate performance degradation caused by irregular access characteristics of graph applications, numerous previous studies focus on designing an efficient memory subsystem [17, 21-28]. Some [21-23] adopt dedicated on-chip data replacement and sophisticated graph partitioning schemes to enhance data reuse and improve locality. Some [17, 24, 25] further alleviate the performance impact of data conflicts occurring in the on-chip BRAM. There are also works aiming to efficiently utilize the bandwidth of on-chip and offchip memories [26-28]. Recently, emerging 3D-stacked memories, e.g., hybrid memory cube (HMC) [29] and high-bandwidth memory (HBM) [30], take the place of commodity memories to boost the power of FPGAs. Some research efforts [31-34] try to exploit the high bandwidth and parallelism of these new devices for accelerating graph application. In addition, in order to support large-scale graph applications, a number of studies construct the multi-FPGA architecture [21, 22]. Alternatives [35-39] employ the CPU-FPGA heterogeneous platform to handle large graphs using two distinct design methodologies. The first category [35, 36, 40] uses the CPU for data preprocessing and task scheduling while the FPGA is responsible for the real computation. Another category [37–39] features CPU-FPGA coprocessing to release the performance potential of heterogeneous platforms.

ASIC-based architecture. Application specific integrated circuit (ASIC) is an integrated circuit customized for specific requirements. It adopts a certain process to interconnect wirings and components (e.g., transistors, resistors, capacitors, and inductors), manufacture them on one or several small semiconductor wafers or dielectric substrates, and then encapsulate them in a tube to become microstructures with specific circuit functions.

Existing ASIC-based accelerators for graph applications typically focus on elaborately constructing application-specific computation units [41–44] and memory hierarchy [45–47] for higher performance and energy efficiency. For example, in the aspect of dedicated computation units, Gra-

phicionado [48] builds graph-processing-friendly pipelines to enable efficient pipelining computations. HyGCN [49] establishes the hybrid execution engines to alleviate irregularity of the aggregation phase and exploits regularity in the combination phase for graph convolutional neural networks. As for the memory hierarchy, GRAMER [50] architects a locality-aware on-chip memory hierarchy, which can handle the substantial random accesses appearing in graph mining applications to minimize the off-chip communications. Ozdal et al. [51] designed dedicated caches for different types of graph data according to the access characteristics. In addition, recent studies aim at exposing flexibility [51–53] and releasing productivity [51, 54, 55] for ASIC-based graph accelerators.

PIM-Based Architecture. Processing-In-Memory (PIM) is a promising technology that addresses the "memory wall" challenge. The key idea is to move the compute units inside the memory, so that the latency and energy consumption of data movement are drastically reduced compared to the conventional von Neumann architecture with a separate computation-memory hierarchy. Existing approaches to enable and implement PIM can fall into two categories: processing using memory (PUM) [56–58] and processing near memory (PNM) [59–63].

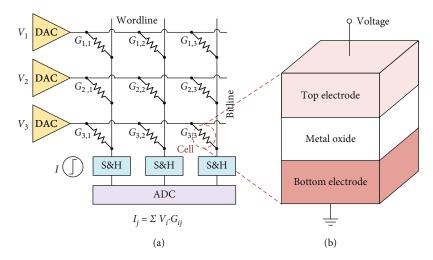

PUM enables memory chips to have the computing ability by exploiting intrinsic operational principles of the memory circuitry [64-66]. Taking resistive random access memory (ReRAM) as an illustration, a ReRAM cell with low read latency and high energy efficiency has an oxide layer sandwiched between two electrodes [67] to store information by changing the resistance across the oxide layer (Figure 1(b)). Many ReRAM cells are organized as an areaefficient crossbar structure to enable high parallelism and memory capacity (Figure 1(a)). ReRAM can perform a matrix-vector multiplication (MVM) operation [68] at one cycle. Specifically, the information stored in the ReRAM cells is programmed to be conductance  $G_{i,j}$ , where conductance is the inverses of resistance and i(j) indicates the wordline (bitline). Digital-to-Analog-Converters (DACs) can convert the input data to analog voltages  $V_i$ , which are applied to the corresponding wordline. Then the current  $Vi \cdot G_{i,j}$  passes through the cell (i, j) into the bitline. Finally, output currents on the same bitline can be accumulated via  $I_i = \sum_i V_i \cdot G_{i,j}$ , and Analog-to-Digital-Converters (ADCs) further convert the results to digital values. Previous studies mainly focus on addressing limited parallelism [69-71] and reducing superfluous ineffectual computations [72–75] for graph applications.

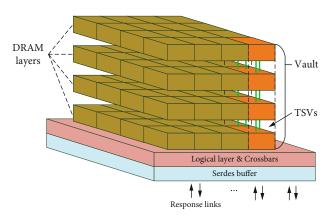

PNM integrates computational logics (e.g., simple inorder cores) inside or nearby the memory. As a representative, Hybrid Memory Cube (HMC) has a logic layer underneath 3D-stacked memories through-silicon vias (TSVs) [76] as shown in Figure 2. Multiple layers of memory and the bottom logic layer are connected together via TSVs, which offer significantly more internal memory bandwidth than the traditional memory channel. Each memory layer contains multiple banks. A vertically connected stack of several banks from different memory layers is called as a vault

FIGURE 1: Illustration of the ReRAM architecture.

FIGURE 2: Illustration of the HMC architecture.

[77]. HMC can benefit from multiple DRAM channels for each vault, exhibiting significantly high memory-level parallelism. Plenty of PNM-based accelerators for graph applications are proposed to exploit the massive parallelism [78–80] and reduce communications [81–83].

# 3. Software Systems Implementation for Graph Analytics

3.1. Software Graph Processing Systems. Many software systems for graph processing are explored on modern general-purpose hardware platforms, and can be classified into two main categories: single-machine graph processing systems and distributed graph processing systems. According to whether the graph data can be stored in memory during processing, these systems can be divided into in-memory graph processing systems and out-of-core graph processing systems. Table 1 summarizes the typical software systems for graph processing. There are four programming models, namely vertex-centric (V), edge-centric (E), path-centric (P), data-centric (D), and two execution models, namely, synchronous (Sync), and asynchronous (Async).

3.1.1. Single-Machine Graph Processing Systems. Single-machine graph processing systems can fully exploit the ability of a single machine to handle graph computation tasks and avoid the expensive network communication overhead in distributed systems. However, such systems are limited by fixed hardware resources and are unable to achieve good scalability, and processing time is typically proportional to the size of the graph data. There are two types of single-machine graph processing systems: in-memory graph processing systems for high-end multicore, large-memory servers, and out-of-core graph processing systems for commercial PCs. The former puts graph data completely into memory during processing, while the latter usually uses disk to store graph data and adopts a certain partitioning strategy to process it in chunks.

Single-machine in-memory graph processing systems often have multiple cores and support very large memory of more than 1 TB, allowing them to handle graph data with hundreds of billions of edges. Compared to single out-of-core graph processing systems, single in-memory graph processing systems keep graph data in memory and can significantly minimize disk I/O overhead. However, single shared memory systems can only scale by increasing the number of CPUs or expanding the memory size.

Ligra [84] is a lightweight shared memory-based single-machine graph processing system, which provides programming abstraction based on edgeMap function, vertexMap function, and vertexSubset type, simplifying the writing of graph processing algorithms. The key idea of Ligra is to accelerate the convergence of the graph algorithms by dynamically switching between the pull and push computation modes during execution based on the size and out-degree of the active vertex subset, but Ligra lacks support for scheduling policies.

The key idea of Galois [85] single-machine graph processing system is to fully exploit the benefits of autonomous scheduling in a data-driven computing mode. Galois designs a machine topology-aware task scheduler and a priority task scheduler with corresponding extension libraries and runtime systems. Galois' flexible and comprehensive programming

Table 1: Overview of typical software systems for graph processing. (IM, PM, EM, DG represent in-memory, programming model, execution model, dynamic graph, respectively, and single machine default to CPU).

| Year | System            | Architecture     | IM  | PM  | EM    | DG  | Main features               |

|------|-------------------|------------------|-----|-----|-------|-----|-----------------------------|

| 2013 | Ligra [84]        | Single machine   | Yes | V   | Sync  | No  | Hybrid computing            |

| 2013 | Galois [85]       | Single machine   | Yes | V   | Async | No  | Priority scheduler          |

| 2015 | Polymer [86]      | Single machine   | Yes | V   | Sync  | No  | NUMA-aware processing       |

| 2017 | HotGraph [87]     | Single machine   | Yes | V   | Async | No  | Hot graph                   |

| 2018 | CGraph [88, 89]   | Single machine   | Yes | V   | Sync  | No  | Correlations-aware          |

| 2019 | GraphBolt [90]    | Single machine   | Yes | V   | Sync  | Yes | Incremental computation     |

| 2021 | DZiG [91]         | Single machine   | Yes | V   | Sync  | Yes | DelZero-aware processing    |

| 2021 | Tripoline [92]    | Single machine   | Yes | V   | Async | Yes | Triangle inequality         |

| 2016 | Gunrock [93]      | Single GPU       | Yes | D   | Sync  | No  | Data-centric PM             |

| 2019 | DiGraph [94]      | Multiple GPUs    | Yes | V   | Async | No  | Dependency-aware processing |

| 2020 | Scaph [95]        | Single GPU       | Yes | V   | Sync  | No  | Value-driven scheduling     |

| 2012 | GraphChi [96]     | Single machine   | No  | V   | Async | No  | Parallel sliding windows    |

| 2013 | X-Stream [97]     | Single machine   | No  | E   | Sync  | No  | Edge-centric PM             |

| 2015 | GridGraph [98]    | Single machine   | No  | E   | Async | No  | Two-level graph partition   |

| 2016 | PathGraph [99]    | Single machine   | No  | P   | Async | No  | Path-centric PM             |

| 2017 | Mosaic [100]      | Single machine   | No  | V/E | Sync  | No  | Hilbert-ordered tiles       |

| 2019 | GraphM [101]      | Single machine   | No  | E   | Sync  | No  | Regularizing traversal path |

| 2022 | EGraph [102]      | Single GPU       | No  | E   | Sync  | Yes | LPS execution model         |

| 2010 | Pregel [103]      | Distributed CPUs | Yes | V   | Sync  | No  | Vertex-centric PM           |

| 2012 | GraphLab [104]    | Distributed CPUs | Yes | V   | Both  | No  | Asynchronous execution      |

| 2012 | PowerGraph [105]  | Distributed CPUs | Yes | V   | Both  | No  | GAS model                   |

| 2015 | PowerSwitch [106] | Distributed CPUs | Yes | V   | Both  | No  | Hybrid computing model      |

| 2014 | Maiter [107]      | Distributed CPUs | Yes | V   | Async | No  | DAIC theory                 |

| 2017 | KickStarter [108] | Distributed CPUs | Yes | V   | Async | Yes | Trimmed approximations      |

| 2021 | Ingress [109]     | Distributed CPUs | Yes | V   | Sync  | Yes | Flexible memorization       |

| 2015 | Chaos [110]       | Distributed CPUs | No  | E   | Sync  | No  | Scale-out graph processing  |

interfaces allow users to build complicated algorithms as easily as feasible.

Polymer [86] is a multicore processing-oriented nonuniform memory access (NUMA) aware graph processing system. The system performs differential allocation of topology data, application data, and system variable runtime state according to the access pattern to reduce remote memory access while converting random remote access to sequential remote access with lightweight vertex replication across NUMA nodes. Furthermore, Polymer further builds a hierarchical barrier to improve parallelism and locality and uses edge-based balanced partitioning strategies and adaptive data structures to improve load balancing.

HotGraph [87] presents an asynchronous graph processing technique based on core graphs to fully utilize the cascade effect and accelerate the convergence of asynchronous graph algorithms. It contains core graph vertices in the graph, or hot vertices, and the paths between them in a data structure called the core graph. Then, HotGraph gives this core graph a high processing priority, so that the state push in the core graph happens faster. On this basis, in order to speed up the local convergence speed of each graph block, HotGraph adopts an alternate data processing strategy to process each graph block.

CGraph [88, 89] proposes an association-aware execution model and a scheduling algorithm based on core subgraphs, which enables concurrent iterative graph processing jobs to effectively share graph structure data and access in cache/memory and effectively reduce the memory access/computation ratio of concurrent iterative graph processing jobs so as to efficiently execute concurrent iterative graph processing jobs and enable the system to obtain higher throughput.

For dynamic graph processing, incremental computation techniques are usually used. GraphBolt [90] incrementally corrects the difference between the original graph result and the real graph for each round by recording the vertex state of one round during the iterative process and combining it with the dependencies on the graph. The vertex state correction, through dependencies, enables GraphBolt to reduce a large number of redundant computations. However, its need to record each round of vertex state for incremental computation also brings a huge storage overhead.

DZiG [91] notes that many incremental graph processing systems are designed with change-driven models in order to reduce redundant computations, which can lead to sparsity in iterative computations. DZiG adapts to graph changes through a sparsity-aware incremental processing

method, while being able to adaptively switch incremental strategies based on the sparsity of the computation. Compared to GraphBolt, DZiG further improves the performance and increases the scale that can handle graph changes simultaneously.

Tripoline [92] points out that existing incremental graph processing systems often rely on a priori knowledge in terms of queries. For instance, KickStarter's [108] incremental queries rely on the source points not changing each time when they are queried, otherwise the dependency trees they maintain would be useless. Tripoline is able to reuse the latter to speed up the former by establishing strict constraints between the evaluation of one graph query and the result of another graph query, which will not depend on any prior knowledge. GPUs have many processing units and abundant bandwidth resources, which can provide a higher parallel computing capability than CPUs, and can efficiently support large-scale graph vertex traversal and update. High concurrency is a characteristic of graph processing. Both the vertex-centric and edge-centric graph computing programming models hide a large amount of data parallel semantics, enabling GPU parallel acceleration. Graph processing is also a data-intensive application, and the bandwidth of hundreds of GB/S provided by GPUs has obvious advantages over CPUs. More graph data can be transmitted per unit time, and the parallel advantages of GPUs can be fully utilized for acceleration. However, GPU-based graph processing acceleration technologies face challenges such as unbalanced workload, low bandwidth utilization, and insufficient memory capacity.

Gunrock [93] designs a general accelerated library for GPU-based graph processing, and proposes a data-centric programming abstraction that combines high-performance GPU computing primitives with optimization strategies for high-level programming models, enabling fast implementation of high-performance graph primitives on GPUs. Gunrock employs a hybrid scheduling strategy to achieve load balancing of computational tasks across different granularities. At the same time, Gunrock implements a hybrid data structure of CSR and edge list to improve the efficiency of aggregated accesses and reduce the extra overhead caused by random accesses.

DiGraph [94] proposes a path-based multi-GPU acceleration method, which represents a directed graph as a set of disjoint directed paths and treats the paths as the basic parallel processing units, enabling efficient propagation of vertex states along the paths under GPU acceleration, thus speeding up convergence. DiGraph also includes a path-dependent perception scheduling strategy, which processes the paths according to the topological order of the path-dependent graph, effectively reducing the redundant processing of graph data and accelerating the convergence of the graph algorithms.

For faster iterative graph processing on GPUs, Asyn-Graph [111] proposes a graph structure-aware asynchronous processing method and a forward-backward path processing mechanism to maximize data parallelism for graph processing on GPUs. The former can efficiently perform parallel state propagation for most vertices on the

GPU and obtain higher GPU utilization by efficiently processing paths between important graph vertices; the latter can process graph vertices on each path asynchronously, which in turn further increases the speed of state propagation along the path while ensuring lower data access costs.

Scaph [95] is a value-driven scalable GPU-accelerated graph processing system that can effectively improve the utilization of GPU bandwidth by differentially scheduling the processing based on the values that partition the subgraphs. Due to Scaph's excellent scalability, its performance advantage can be progressively increased as computational resources become more readily available.

Subway [112] proposes a fast subgraph generation algorithm, which generates subgraphs of the graph data to be processed quickly by GPU acceleration before each iteration, and then loads the subgraphs into the GPU for processing, thus effectively reducing the data transfer overhead between the CPU and GPU. Additionally, Subway reduces the number of data transfers by delaying the synchronization between the subgraph data in the GPU memory and the graph data in the CPU memory, which further improves the graph processing performance.

With the rapid expansion of graph data size, many single-machine graph processing systems use external memory, such as disks, to store very large scale graph data. The I/O bandwidth limitation of external memory such as disks has become the performance bottleneck of single-machine out-of-core graph processing systems, and it is a challenge to reduce random accesses during graph computing.

GraphChi [96] is the first disk-based graph processing system that proposes the Parallel Sliding Windows (PSW) technique to optimize the access to disk during graph computation. GraphChi preprocesses edge data into shards by a specific graph partitioning strategy, and then the PSW asynchronous computation model is used to process the shards, thus effectively reducing random disk accesses and improving system performance.

X-Stream [97] proposes an edge-centric computation idea to process edges in external memory or in-memory in a streaming manner to improve the continuity of access to memory, thus making full use of the bandwidth of storage devices to improve performance. X-Stream designs a streaming partition mechanism to divide graph data, and then uses an edge-centric scatter-gather computing model to stream the graph partitions, maximizing throughput through streaming access to edges.

GridGraph [98] proposes a two-level graph partitioning strategy, which divides the graph data finely in the preprocessing stage, and then further divides the edge data dynamically at runtime to improve memory access efficiency. At the same time, GridGraph uses dual sliding window technology to stream edge data to reduce the I/O required for computation. In addition, GridGraph also provides a flexible and selective scheduling strategy, which can further reduce graph data I/O.

PathGraph [99] proposes a path-centric graph computing model, which can effectively improve the locality of memory and disk when executing iterative graph algorithms on large-scale graphs. Moreover, the path-centric compressed

storage structure further improves the continuity of data access, thereby accelerating the execution of graph computing tasks.

Mosaic [100] is a heterogeneous graph processing system that scales horizontally and vertically through a hybrid execution model. The main processor is responsible for vertex-centric operations on the global graph and the coprocessor is responsible for completing edge-centric operations on the local graph, capable of supporting graph computing on trillions of edges.

LUMOS [113] proposes a dependency-driven graph processing technique that actively propagates values between iterations through unordered execution while providing synchronous processing guarantees. The cross-iteration value propagation mechanism of LUMOS efficiently identifies future dependencies and can actively compute the values of dependencies without sacrificing disk locality, which can diminish the number of graph data that needs to be loaded in subsequent iterations and speed up graph processing.

In order to optimize the execution efficiency of graph computing tasks, DGraph [114] scales each strongly connected component of the graph into abstract graph vertices according to the dependencies between graph vertices. The graph is transformed into an abstract directed acyclic graph, and then the directed acyclic graph is divided into multiple layers so that there is no interdependence between the strongly connected components of each layer. Then, each strongly connected component is processed in parallel according to the level number so that a high number of graph vertices only need to be processed a few times to converge, greatly reducing the data access costs and redundant update times.

Wonderland [115] is a graph processing system based on graph abstraction, which can efficiently extract graph abstractions from raw graph data under specified memory constraints, and accelerate disjoint graph partitioning on disk through graph abstraction interval message propagation to improve graph processing performance. Wonderland also includes a priority scheduling strategy based on graph abstraction, which can effectively accelerate the convergence of graph algorithms.

Congra [116] and CongraPlus [117] explored the scheduling problem of concurrent graph computing requests, and designed a set of memory bandwidth-efficient singlemachine graph computing scheduling strategies on the shared memory architecture. CongraPlus graph computation requests are implemented based on the Ligra framework. This technology obtains information about graph processing requests through offline sampling. In the running phase, CongraPlus first distributes requests to the local scheduler evenly through global request allocation, and then uses an iterative ascent algorithm to calculate the optimal number of threads required for each request. During this process, the system ensures that concurrently executed requests do not over-compete for memory bandwidth and uses the LookAhead algorithm to provide better performance for heavily loaded requests.

GraphM [101] is an effective storage system which can be easily embedded into the existing graph computing system and make full use of the data access similarity of concurrent graph computing tasks, allowing the graph structure data to be regularly flowed into memory/cache and shared by concurrent graph computing tasks, improving the throughput of concurrent graph computing tasks by reducing data access and storage overhead. Subsequently, GraphSO [118] adopts a fine-grained graph data management mechanism and uses an adaptive data repartitioning strategy and a structure-aware graph data caching mechanism at runtime to further reduce redundant I/O for concurrent graph computing tasks overhead and improve system throughput.

EGraph [102] is a GPU-based dynamic graph processing system that can be integrated into existing GPU out-of-core static graph processing systems and efficiently utilizes GPU resources to support concurrent processing of different snapshots of dynamic graphs. Unlike existing approaches, EGraph proposes an efficient Loading-Processing-Switching (LPS) execution model. It achieves efficient execution of temporal iterative graph processing tasks by making full use of the data access similarity between temporal iterative graph processing tasks to effectively reduce the CPU-GPU data transfer overhead and ensure higher GPU utilization.

3.1.2. Distributed Graph Processing Systems. A distributed graph computing system consists of multiple computing nodes, each of which has its own memory and external memory. Therefore, compared to single-machine graph computing systems, distributed graph processing systems are less limited by hardware in terms of scalability. However, in a distributed graph processing system, graph data is distributed to multiple nodes for processing. Therefore, the data partitioning mechanism has a great influence on the performance of the distributed graph processing system, and it is a challenge to design an appropriate data partitioning strategy. Meanwhile, the communication between computing nodes becomes a performance bottleneck, and the system's overall performance and the scale of data processing are limited by the network bandwidth.

Most distributed graph processing systems are distributed in-memory graph processing systems, in which all graph data is completely loaded into memory for processing.

Pregel [103] is one of the earliest distributed in-memory graph processing systems, which uses the batch synchronous parallel (BSP) model for processing graph data and proposes a vertex-centric computing framework that represents the graph algorithm as a series of iterations, where each vertex modifies its own state and the state of its output edges based on the messages it has received from previous iteration and sends the messages to other vertices. The vertex-centric computing framework is extremely expressive and can implement a large variety of graph algorithms.

Many distributed in-memory graph processing systems are extended with Pregel [103]. GraphLab [104] supports asynchronous execution of graph algorithms while ensuring data consistency, and this asynchronous model tends to have faster convergence and lower synchronization costs than synchronous models. However, GraphLab still suffers from vertex degree skew. GraphX [119] is a graph processing

framework on Apache Spark that combines the advantages of a dedicated graph processing system with those of a distributed data streaming system to provide a set of composable graph abstractions on a distributed data streaming system to implement and execute iterative graph algorithms efficiently.

To address the workload imbalance and other problems associated with power-law graphs, PowerGraph [105] adopts the Gather-Apply-Scatter (GAS) computation model to decompose the vertex program into multiple stages, allowing the computation to be more evenly distributed across the cluster. At the same time, vertex partitioning and a series of fast heuristics are employed to reduce the storage and communication overhead of power-law graphs on distributed clusters. PowerGraph can support the BSP computation model of Pregel [103] and the asynchronous computation model of GraphLab [104].

PowerSwitch [106] and PowerLyra [120] are designed based on the distributed graph computing system Powergraph [105]. Power-Switch proposes a hybrid computing model, which can automatically switch between asynchronous and synchronous execution modes during parallel graph computing processing to obtain the best performance. PowerLyra employs different graph division strategies and graph computation schemes for high-degree and low-degree vertices to improve system efficiency.

Gemini [121] is a computation-centric graph processing system, which applies the hybrid Push/Pull computing paradigm in distributed scenarios, and adopts a chunk-based graph partitioning strategy that exhibits good data locality at multiple levels of parallelism. Gemini builds a low-cost distributed design on the basis of optimizing the computing efficiency of a single node, which effectively improves the utilization of system resources.

Grape [122] is a graph computing system that can automatically convert serial algorithms into parallel algorithms. Its main benefit is that serial algorithms' logic does not need to be changed. This significantly lessens the challenge of parallel programming in graph computing since it can be done in parallel by putting it into Grape as a whole. In addition, since Grape divides vertices into a specified number of fragments, the vertices on each fragment can adopt a serial algorithm, and then parallelize the algorithm to support data partition parallelism so that optimization strategies developed for serial algorithms can be implemented in Grape. These optimizations are difficult to use directly in ordinary vertex-centric models.

To speed the convergence of graph computing tasks, Maiter [107] proposed the difference-based cumulative iterative computation (DAIC) theory, where each vertex only propagates and accumulates the updated value instead of the full value of the vertex, which can be executed asynchronously and efficiently. The graph iterative algorithm uses less iterative computation overhead to reach a convergent state, and rigorously proves the correctness of the DAIC computation.

To further accelerate asynchronous graph processing on distributed platforms, FBSGraph [123] proposes an efficient forward and backward scanning execution approach, which can greatly enhance the state propagation efficiency of asynchronous graph processing. FBSGraph also includes a static prioritization scheme, which can effectively reduce the communication overhead of asynchronous graph processing on distributed platforms, and further improve the convergence speed of asynchronous graph algorithms.

PowerLog [124] further explores the theoretical underpinnings of whether monotonic or nonmonotonic programs can be performed correctly asynchronously and incrementally and develops a conditional verification tool to automatically check whether the program satisfies this condition. Based on this, PowerLog designs a unified distributed synchronous and asynchronous engine. When executing recursive aggregation programs, it realizes adaptive asynchronous and synchronous execution modes by dynamically adjusting the frequency of message propagation to minimize program execution time. PowerLog's analytical approach is the basis of incremental computing for many graph processing and graph neural networks.

For efficient processing of streaming graphs, Kineograph [125] designs a distributed in-memory graph storage system to generate a reliable and consistent series of snapshots at regular intervals and uses a graph computation engine that supports incremental iterative propagation to process the snapshots to obtain real-time computation results. The core idea of real-time computation results is to interleave iterative computation and batch updates of graphs. Iterative computation maintains the intermediate computation results of the most recent version of the graph, and when a query is received, iterative computation is performed directly from the intermediate results to obtain the exact computation results of the current version of the graph after the batch update.

Tornado [126] optimizes real-time iterative graph processing on distributed platforms. It proposes an approximation method to enhance the timeliness of graph processing and designs a novel bounded asynchronous iterative processing model that can ensure the correctness of graph processing results and achieve efficient fine-grained updates.

During dynamic graph processing, changes in graph structure brought about by edge deletion may lead to invalidation or performance degradation of intermediate results of graph computation. For this reason, KickStarter [108] proposes a runtime technique to address the challenges posed by edge deletion. The key idea is to precisely identify the vertices affected by edge deletion based on inter-vertex dependencies and adjust the state values of these vertices to an estimate close to the convergence value. This runtime technique of tracking and adjusting vertex state values ensures that the computation yields correct results and accelerates the convergence of the graph algorithm.

Aiming at incremental computing for large-scale dynamic graphs, Ingress [109] can automatically realize the incrementalization of vertex-centric graph algorithms, and is equipped with four different computing state memory strategies. The strategy applies to the sufficient conditions of the graph algorithm, and the system can automatically select the optimal memory strategy according to the algorithm logic specified by the user.

| TABLE 2: Overview of software systems for graph mining. (PA | GTS, MPO represent pattern-aware, graph-traversal strategy, multipattern |

|-------------------------------------------------------------|--------------------------------------------------------------------------|

| optimization, respectively).                                |                                                                          |

| Year | System                     | Architecture                  | PA  | GTS    | MPO | Main features                            |

|------|----------------------------|-------------------------------|-----|--------|-----|------------------------------------------|

| 2015 | Arabesque [127]            | Distributed CPUs              | No  | BFS    | No  | Embedding-centric model                  |

| 2016 | ScaleMine [128]            | Distributed CPUs              | No  | BFS    | No  | Scalable and parallel                    |

| 2018 | G-Miner [129]              | Distributed CPUs              | No  | BFS    | No  | Task pipeline                            |

| 2018 | RStream [130]              | Single machine                | No  | BFS    | No  | GRAS model                               |

| 2019 | Fractal [131]              | Distributed CPUs              | No  | DFS    | No  | DFS exploration                          |

| 2020 | G-thinker [132]            | Distributed CPUs              | No  | BFS    | No  | Vertex caching<br>Task scheduling        |

| 2020 | Pangolin [133]             | Single machine<br>(CPU & GPU) | No  | BFS    | No  | Efficient and flexible                   |

| 2021 | aDFS [134]                 | Distributed CPUs              | No  | Hybrid | No  | Almost-DFS exploration                   |

| 2019 | AutoMine [135]             | Single machine                | Yes | DFS    | Yes | Compilation techniques<br>Matching order |

| 2021 | GraphZero [136]            | Single machine                | Yes | DFS    | Yes | Symmetry order                           |

| 2020 | Peregrine [137]            | Single machine                | Yes | DFS    | No  | Matching order<br>Symmetry order         |

| 2020 | GraphPi [138]              | Distributed CPUs              | Yes | DFS    | No  | Optimal order                            |

| 2020 | DwarvesGraph [139]         | Single machine                | Yes | DFS    | No  | Pattern decomposition                    |

| 2021 | Kudu [140]                 | Distributed CPUs              | Yes | Hybrid | No  | Extendable embedding BFS-DFS exploration |

| 2021 | Sandslash [141]            | Single machine                | Yes | DFS    | No  | Two-level optimizations                  |

| 2021 | SumPA [142]                | Single machine                | Yes | DFS    | Yes | Pattern abstraction                      |

| 2022 | G <sup>2</sup> Miner [143] | Multiple GPUs                 | Yes | Hybrid | Yes | Input-aware<br>Architecture-aware        |

The distributed out-of-core graph processing system expands the single-machine out-of-core graph processing system into a distributed cluster, thereby further expanding the scale of graph data. Based on X-Stream [97], Chaos [110] is currently the only distributed out-of-core graph processing system, and extends single-machine out-of-memory graph computation to multiple machines. It is composed of computing subsystems. Each machine has a storage subsystem as a storage engine, which provides vertices, edges, and updates for the computation subsystem. Chaos realizes parallel execution and sequential storage access by adjusting the X-Stream stream partition and achieves multimachine load balancing through random work stealing technology.

3.2. Software Graph Mining Systems. Recently, several software systems have been proposed to solve the graph mining problem. They search for subgraphs that satisfy the conditions of the algorithm in the input graph G. The process of finding subgraphs can be modeled with a search tree where each node represents a subgraph, and the subgraphs at the k+1 level are expanded from the subgraphs at the k level. Based on the model, these systems can be classified by programming model into two main types: pattern – oblivious and pattern – aware, also called embedding – centric and set – centric. They also adopt a variety of different techniques, such as graph-traversal strategy and multipattern optimization, to improve the performance of graph mining

problems. Table 2 summarizes the software systems for graph mining.

#### 3.2.1. Programming Model

(1) Pattern-Oblivious Programming Model. Pattern-oblivious systems [127–131, 133, 134] adopt the embedding-centric approach to solve the graph mining problem. They establish a search tree to represent the partial embeddings (nonleaf nodes) and final embeddings (leaf nodes). For the partial embeddings, some pruning techniques are employed to prevent duplication and unnecessary exploration. For the final embeddings, expensive isomorphic tests are applied to check if they are isomorphic to the pattern. Arabesque [127], the first distributed graph mining system, uses BFS to explore the search tree based on the BSP model, and proposes the coordination-free exploration strategy to avoid redundant exploration. However, Arabesque suffers from high memory and IO costs and synchronization overhead.

Memory and IO costs. Although BFS exploration provides high parallelism, the number of subgraphs increases exponentially with the pattern's size. When the input graph is large, keeping all subgraphs in memory is impractical, and employs out-of-core processing, which may cause an IO bottleneck. To keep CPU cores occupied while waiting for data, G-thinker [132] maintains a pool of active tasks that can be processed at any time. In this way, while some tasks are

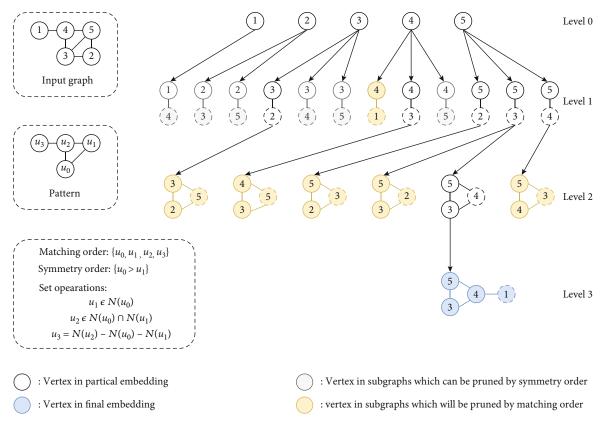

FIGURE 3: A four-level subgraph search tree for pattern-aware graph mining algorithm.

waiting for data, other tasks can continue their computations. Furthermore, it implements a novel vertex cache to support highly concurrent vertex accesses to minimize redundant requests. To reduce memory consumption, Fractal [131] adopts the DFS method to enumerate embeddings.

Synchronization overhead. The BSP model requires synchronization between supersteps, which leads to the straggler problem, lowering hardware utilization of distributed graph mining systems. To remove the synchronization barrier, G-Miner [129] proposes a novel task-pipeline design which can asynchronously process CPU computation, network communication, and disk I/O.

ScaleMine [128] introduces a novel two-phase solution to support the FSM algorithm in a single large graph with scalability and parallelism. In the first phase, it adopts an approximate approach to efficiently identify subgraphs with high probability. In the next phase, the exact solution is computed by utilizing the collected information from the first phase to ensure excellent load balancing and improve parallelism.

To overcome the drawbacks of conventional distributed mining systems, such as large startup and communication overhead and underutilization of CPU resources, RStream [130] develops the first single-machine, disk-based, out-of-core graph mining system. Based on relational algebra, RStream provides a rich programming model (named GRAS) to enable a variety of graph mining algorithms and efficient implementations of relational operations (particularly join) for graphs.

Existing mining systems, such as Arabesque and RStream, have limited performance because they are mainly focused on generality rather than application-specific customization and implementations of parallel operations and data structures. To solve the issues, Pangolin [133] provides high-level abstractions for the processing of graph mining on CPU and GPU and enables application-specific customization. Besides, efficient parallel operations and data structures are designed to improve hardware utilization.

(2) Pattern-Aware Programming Model. Existing pattern-oblivious graph mining systems made a lot of effort to solve several significant problems and achieved remarkable performance improvements. However, there are still issues with the costly overhead of subgraph isomorphism tests and pruning search space. To address the issues, the pattern-aware solution [135–138] analyzes the structure of the pattern and generates a matching order [137] and a symmetry order [136] to eliminate isomorphism tests and repetitive enumeration. The pattern-aware algorithm for mining a tailed triangle pattern with four vertices is shown in Figure 3.

*Matching Order.* Matching order is the search order of vertices in the pattern when performing graph mining. For example, in Figure 3, a matching order of the tailed triangle pattern is  $\{u_0, u_1, u_2, u_3\}$ , indicating that  $u_i$  is ancestor of  $u_j$  and searches prior to  $u_j$  only when i > j. The yellow colored subgraphs in Figure 3 can be pruned by the matching order, because the input graph does not contain the vertex that the

matching order wants to explore in the next step. For example, the subgraph  $\{u_0,u_1\}=\{4,1\}$  expends the next vertex  $u_2$  of the pattern which is a common neighbor of  $u_0$  and  $u_1$ . Since the intersection set of N(4) and N(1) in the input graph is empty, the subgraph  $\{4,1\}$  has no branches that meet the matching order and can be pruned. More importantly, isomorphism tests can be avoided using matching order, because the final embeddings always match pattern.

Symmetry Order. Although employing matching order can eliminate isomorphism tests and prune search space, a certain subgraph can be explored multiple times due to the symmetry of vertices in the pattern. As shown in Figure 3,  $u_0$  and  $u_1$  of the pattern are symmetric, and the subgraphs  $\{2,3\}$  and  $\{3,2\}$  are identical subgraphs which also called automorphisms. To eliminate duplication of enumerating these embeddings, symmetry breaking method establishes a symmetry order among the vertices of the pattern. For instance, in Figure 3, the symmetry order  $u_0 > u_1$  is employed to prune the search space and ensure uniqueness. In particular, the grey colored subgraphs in Figure 3 such as the subgraph  $\{2,3\}$ , which is automorphic to the subgraph  $\{3,2\}$ , are pruned by the restriction of  $u_0 > u_1$ .

Optimal order. Previous pattern-aware systems adopted the matching order and symmetry order to avoid isomorphism tests and redundant enumeration. However, different matching orders and symmetry orders have an important influence on the performance of the graph mining system. To address the problem, GraphPi [138] first designs algorithms to generate multiple sets of matching order and symmetry order. Then, it discovers the optimal combination of matching order and symmetry order based on a precise performance prediction model. Furthermore, GraphPi leverages the technique of Inclusion-Exclusion Principle (IEP) to optimize the algorithms that just count the embeddings' number.

The execution time of embedding enumeration increases dramatically as the pattern size grows. To address the challenge, DwarvesGraph [139] develops a high-performance system using pattern decomposition techniques, which break down a large pattern into a number of smaller subpatterns, and then compute each of them separately. To support various applications, DwarvesGraph introduces a novel partial-embedding-centric programming model. To decrease memory consumption and random access, DwarvesGraph proposes an efficient on-the-fly aggregation of subpatterns embeddings. DwarvesGraph also designs a compiler that employs conventional and loop rewriting optimization and a novel lightweight cost model to estimate the performance of an algorithm implementation candidate.

Sandslash [141] provides a two-level (high- and low-level) programming model and corresponding optimizations, while earlier systems only focused on one level (i.e. either high-level [135, 137] or low-level [130, 133]). The high-level programming interface provides effective search strategies, data representations, and high-level optimizations such as matching order. The low-level programming interface allows the programmers to express algorithm-specific optimizations. Sandslash also flexibly explores combinations of optimizations to enhance performance.

3.2.2. Graph-Traversal Strategy. Exploration of the search tree generally follows one of two typical graph-traversal strategies: BFS or DFS, but different graph-traversal strategies have different parallelism and memory consumption. BFS explores the search tree level by level and maintains a list of intermediate subgraphs at each level that can be processed in parallel. Although BFS enables tremendous parallelism, it suffers from memory consumption due to the size of intermediate subgraphs grows exponentially. DFS reduces the size of intermediate subgraphs, but it is difficult to parallelize because of the data dependency, and has poor locality because of irregular memory access. To take advantage of the best of both strategies, many systems [134, 140, 143] employ a DFS-BFS hybrid strategy.

aDFS [134] proposes an almost DFS graph exploration strategy with a high degree of parallelism and constrained runtime memory consumption. In particular, threads in aDFS mainly prioritize DFS exploration and switch to BFS when waiting for the required data (e.g., edges on a remote machine) or when the exploration reveals low parallelism (e.g., a few intermediate subgraphs) that the runtime can identify.

The task granularity and execution schedule influence the efficiency of a distributed graph mining system with partitioned graph. To reduce task granularity and enable efficient scheduling, Kudu [140] proposes a well-defined abstraction of extendable embedding which has high expression for graph mining algorithms and enables finegrained task scheduling and a BFS-DFS hybrid exploring approach which produces appropriate concurrent tasks with limited memory consumption, respectively. Specifically, the BFS-DFS hybrid exploration adopts DFS with a chunk granularity.

For problems that use domain support, such as FSM,  $G^2$  Miner [143] proposes a bounded BFS search to fully utilize the GPU. It initially employs BFS search to generate massive parallelism, and then partitions the intermediate subgraphs into blocks, each of which can reside in memory when the intermediate subgraphs cannot fit in memory. After that, the subgraphs can be processed block by block. For the loading imbalance of DFS,  $G^2$  Miner employs edge parallelism, which maps the subtree rooted at each edge at level 1 of the search tree to one task, instead of vertex parallelism (explanation similar to edge parallelism) to reduce task granularity and provide more parallelism.

3.2.3. Multipattern Optimization. Unlike a single-pattern problem, which only mines one single pattern at a time, a multipattern problem finds multiple patterns simultaneously. Running multipattern problems could result in redundant computations [142] and low hardware utilization [143]. To overcome these issues, graph mining systems such as AutoMine [135], G<sup>2</sup>Miner [143], and SumPA [142] propose a variety of optimizations, the key insight of which is to merge multiple patterns that share the same subpattern to enjoy sharing.

AutoMine [135] first generates a schedule for each pattern, which is a sequence of set operations, and then combined those schedules to form the merged schedule.

| Year | System               | Architecture     | IM  | Baselines                  | Main features                                                                             |

|------|----------------------|------------------|-----|----------------------------|-------------------------------------------------------------------------------------------|

| 2019 | DGL [144]            | Single GPU       | Yes | PyG                        | Compatible with multiple backends<br>Message-passing parallelism                          |

| 2019 | PyG [145]            | Single GPU       | Yes | DGL                        | Optimization of sparse operations                                                         |

| 2020 | FeatGraph [146]      | Single GPU       | Yes | Gunrock                    | Optimization of matrix mult<br>User-defined functions                                     |

| 2020 | $G^{3}$ [147]        | Single GPU       | Yes | PyTorch<br>TensorFlow      | Using graph processing systems to support graph-structured operations                     |

| 2021 | GNNAdvisor [148]     | Single GPU       | Yes | DGL, PyG<br>NeuGraph [149] | Profiling of GNN model and graph<br>2D workload management                                |

| 2021 | PyTorch-direct [150] | Multiple GPUs    | No  | PyTorch                    | Zero-copy programming model                                                               |

| 2022 | GNNLab [151]         | Multiple GPUs    | No  | DGL, PyG                   | Factored space sharing design<br>Presampling based caching policy                         |

| 2021 | P3 [152]             | Distributed GPUs | Yes | DGL, ROC [153]             | Eliminating high communication and partitioning overheads Pipelined push-pull parallelism |

| 2021 | DistGNN [154]        | Distributed CPUs | Yes | DGL                        | Full-batch GNN training on CPUs mitigating communication bottlenecks                      |

| 2022 | ByteGNN [155]        | Distributed CPUs | Yes | DGL, Euler                 | Two-level scheduling strategy<br>New graph partitioning algorithm                         |

| 2022 | NeutronStar [156]    | Distributed GPUs | Yes | DGL, ROC                   | Hybrid dependency management                                                              |

TABLE 3: Overview of typical software systems for graph learning.

Specifically, AutoMine analyzes prefixes of schedules, and overlapped prefixes can be shared to avoid repetitive enumeration and contribute to data reuse. The common search paths of schedules first begin to converge, and then diverge at some level k where the paths differ.

Unfortunately, the sharing the prefix technique in Auto-Mine only eliminates a small proportion of redundant computations, since the matching order must be the same even though prefixes of schedules construct the same subgraphs. SumPA [142] presents a pattern abstraction technique based on pattern similarity to guide pattern mining and eliminate (totally and partially) redundant computations. Specifically, SumPA proposes a redundancy criterion called Shared Connected Subpattern (SCS) to characterize redundant computation. According to the SCS similarity, it extracts a few sample abstract patterns from numerous complex patterns.

G<sup>2</sup>Miner [143] employs a kernel fission technique to improve hardware utilization of mining multipatterns simultaneously on GPU. G<sup>2</sup>Miner analyses multiple patterns to identify those patterns that share the same subpattern, and then they can share the same workflow by merging into the same CUDA kernel. In contrast, G<sup>2</sup>Miner generates distinct kernels for those patterns that do not share the same subpatterns.

3.3. Software Graph Learning Systems. As one of the most popular research directions in the field of artificial intelligence in recent years, graph neural network has produced a large number of different algorithms. Many enterprises and research teams have carried out research and development work on the framework and extension library of graph-oriented neural network based on a common platform. Because graph neural network applications and tradi-

tional neural network applications have similarities and differences in many aspects of implementation methods, many existing works are expanded based on the mature neural network frameworks, such as PyTorch and Tensorflow, to form a new framework supporting graph neural network applications. These frameworks and extension libraries support many different graph neural network algorithms, most of which are open source, and it is convenient for users to construct graph neural network flexibly. The mainstream graph neural network framework and extension library will be introduced in the following. Table 3 gives an overview of typical software systems for graph learning.

3.3.1. Single-Machine Graph Neural Network System. A typical GNN system is divided into a data module and a computation module. Among them, the data module is mainly responsible for IO and preprocessing of data, and the computation module is mainly responsible for training and inference of algorithmic models. GNN systems with a single GPU are the first to receive attention in the early development of GNN acceleration systems. This is because in the case of relatively small graph structure and feature vector data, which can be stored directly in the GPU memory. Regarding this, a large amount of work has emerged, such as Deep Graph Learning (DGL) [144], PyTorch Geometric (PyG) [145], GNNAdvisor [148], and G³ [147].

DGL [144] is one of the mainstream academic GNN programming frameworks currently integrated in mainstream neural network system architectures, such as PyTorch, Tensorflow, and MXNet. DGL follows the Message Passing Neural Network computational paradigm proposed by Google [157] to accomplish GNN training and inference. This computational paradigm contains three main

propagation phases, i.e., Message Passing Phase, Reduce Phase, and Update Phase, and its propagation formula can be expressed by the following equation  $(y_{i'})$  denotes the output result of vertex i;  $y_i$  and  $y_j$  denote the input feature, respectively;  $e_{i,j}$  denotes the feature of edge i to j;  $\varnothing$  denotes the aggregation formula;  $y_{\wp}$  denotes the activation function).

$$y_i' = \gamma_{\Theta} \left( y_{i,j \in N(i)} \varnothing \left( y_i, y_j, e_{i,j} \right) \right). \tag{1}$$

Message Passing Phase, i.e., for each edge on the graph, the message to be propagated for each edge is obtained by computing the features on the edge and the features of the two nodes on the edge.

$$\emptyset(y_i, y_j, e_{i,j}).$$

(2)

Reduce Phase is mainly computed for graph vertices, each vertex aggregates the messages on the edges by the reduce function, where the reduce function can be summation, maximum, minimum, and mean, etc.

$$j \in N(i)$$

(3)

Update Phase is also computed for graph vertices, and each vertex is updated by using the update function to update the feature vector of that vertex using the information of the previous layer of that vertex and the aggregated information.

$$\gamma_{\Theta}$$

for each node. (4)

Moreover, DGL mainly adopts the graph-centric computation model, which means that the propagation computation and vertex/edge computation on the graph are implemented through the entire graph itself. To reduce the memory space occupied by the message tensor, DGL also employs message fusion techniques to merge multiple messages into a single message. However, DGL is based on the deep learning framework PyTorch and is developed with a graph manipulation module on top of it, which itself is less optimized for graph manipulation during GNN execution.

Similar to DGL, PyG [145] is also a GNN framework built on Python to model and train deep learning on graph-structured data. However, PyG provides optimization of sparse operations during GNN execution compared to DGL and employs a dedicated CUDA kernel to achieve efficient training. With PyG's defined message-passing interface, the user only needs to define the message and update functions and select the corresponding aggregation function functions, such as accumulation, maximum, and minimum, to define new GNN models.

Compared with the mainstream frameworks such as DGL and PyG, FeatGraph [146] is more concerned with GNN sparse operations, which is due to the fact that the GNN aggregation stage requires multiplying the graph feature vector matrix by the graph adjacency matrix. FeatGraph innovatively proposes the optimization of feature vector cuts

and adopts a new graph partitioning method, which is a super sparse operation. FeatGraph also supports User-Definition Functions (UDFs) for different GNN models of edge aggregation and vertex aggregation functions for different GNN models. However, FeatGraph uses the full-batch training method because it needs to store all data in GPU memory.

PyTorch-direct [150] proposes a large-scale GNN framework based on zero-copy. The sparse node features stored in the CPU are the main reason for slow data loading in large-scale GNN training. Compared with explicit copy, which is suitable for transferring large blocks of contiguous memory, zero-copy is more suitable for dealing with random sparse access. However, the simple implementation of the zero-copy access model will bring the disadvantages of high latency and low bandwidth. Aiming at the shortcomings of zero-copy, it proposes a zero-copy programming model that ensures data access merging and alignment as much as possible.

Existing GNN acceleration systems use traditional deep learning frameworks as backends, such as DGL and PyG, and then add a graph engine module to support graph operations during GNN execution. However, G³ [147] believes that the main reason for the inefficiency of the GNN execution process is the irregular traversal of graph topology and feature vectors in graph operations, so G³ uses Gunrock [93] as the backend. It extends the existing automatic differentiation and neural network operators and other operations. Through Gunrock's own graph operation optimization technology, the efficiency of GNN training and inference is greatly improved.

GNNAdvisor [148] is a flexible and effective runtime system designed to accelerate GNNs on GPUs. It performs online analysis of the input graph and GNN operations to provide guidance to GPU-based workload and memory management agents. Specifically, GNNAdvisor first investigates and determines a number of performance-relevant characteristics from both the input graph and the GNN model. Then, GNNAdvisor provides an extremely effective 2D workload management to increase GPU performance and utilization in a variety of application scenarios. Finally, based on the community features of the graph, GNNAdvisor adopts a combination of node renumbering and reclassification algorithms to reduce memory access.

GNNLab [151] summarizes the minibatch training method based on graph sampling into three stages: sample, extract, and train. When using the GPU to accelerate the extract stage, the features of frequently accessed vertices are loaded into the GPU memory in advance to reduce the amount of feature data copied, thereby accelerating the extract stage. GNNLab designed a method based on space sharing, in which the training process is divided into two parts, with the Sampler in charge of the Sample stage and the Trainer in charge of the Extract and Train stages. In terms of cache strategy, GNNLab proposes a cache strategy based on presampling, which performs several rounds of graph sampling processes in advance, and then loads the features of the vertices with the highest number of samples during the presampling process into the GPU memory in advance.

3.3.2. Distributed Graph Neural Network System. The mainstream single-machine GPU GNN systems save all data in the GPU memory for GNN training and inference. However, in practical application scenarios, the graphs of GNN training and inference are huge. For graphs with a scale of billions or even tens of billions of vertices, it is impossible to store all data in the memory of a single node at one time. Therefore, it is critical to adopt a distributed GNN system to accelerate the efficiency of large-scale GNNs. At present, the typical distributed GNN systems mainly include DistGNN [154], Aligraph [158], and P3 [152].

Euler [159] uses the Tensorflow deep learning framework as the backend and extends support for the distributed CPU GNN framework. The Euler framework mainly includes three main modules: graph operation module, aggregation operator, and algorithm implementation module to rapidly expand the GNN model. Among them, the graph operation module is responsible for the storage of graph structure data and its feature vector data. The aggregation operations on graph vertices or edges, such as globally weighted sampling vertices and edges. In the algorithm implementation module, Euler integrates a variety of common GNN algorithms, such as Scalable-GCN, a general algorithm for accelerating GNN tasks. However, Euler needs to cache the graph vertices and their K-hop neighbor vertices at one time.

P3 [152] is a distributed framework for large-scale GNN training. It focuses on reducing the network communication time and traffic of the vertex feature vector of the graph when using the minibatch training method. Different from traditional DNN distributed training, the graph structure used in GNN training is associative, and graph vertices or edges will have high-dimensional feature vectors. P3 innovatively proposes a pipeline-based push-pull training method, which stores graph structure data and eigenvector data separately, and divides the eigenvector matrix into columns. The column-wise segmentation of the eigenvectors means that for each node, there will be some dimensions of the complete eigenvector matrix for all vertices, and there is no need to pay attention to any graph distribution, so it does not need to be expensive to remote the machine node pulls the required feature vector data. Similarly, P3 also joins the pipeline parallel design, covering the network communica-

DistGNN [154] is optimized based on DGL to support GNN training in full-batch mode efficiently on CPU clusters. DsitGNN optimizes DGL's aggregation primitives to speed up aggregation operations through chunked caching, dynamic thread scheduling, and optimized loop execution using LIBXSMM. To reduce traffic, DistGNN uses a vertexcut based graph partitioning algorithm. At the same time, to further reduce the communication's impact on the training performance during the vertex aggregation operation on the graph, DistGNN introduces a delayed aggregation update strategy of cutting points, overlapping communication and calculation, and hiding the communication overhead during aggregation.

Dorylus [160] is a distributed GNN training framework that can scale to billion-edge graphs using low-cost

resources. To solve the problem of limited memory of GPUs, which does not scale to large graphs, Dorylus leverages serverless computing to increase scalability, and the key idea is computational separation. Computational separation can enable a pipeline where computational and tensor-parallel tasks on the graph can completely overlap. It divides the training pipeline into a set of fine-grained training pipelines according to the type of data processed by the training pipeline.

Aligraph [158] is a comprehensive distributed GNN framework built on the Tensorflow deep learning framework, which can process very large-scale graphs. It mainly consists of three parts, namely, (1) storage, which implements partitioning using multiple algorithms depending on the characteristics of the graph to minimize data movement; (2) sampling, which allows for the definition of algorithms, and custom sampling of relevant node neighborhoods; (3) operators, which implements combination and aggregation functions.

In order to optimize data communication between multiple GPUs, the distributed graph communication library DGCL [161] is proposed mainly for efficient GNN training. At the core of DGCL is a communication planning algorithm tailored for GNN training, which collectively takes into account the full utilization of fast links, converged communication, avoidance of contention, and balancing the load on different links. Existing single-GPU GNN systems can be easily extended to distributed training using DGCL.

ByteGNN [155] is a GNN training system based on GraphLearn. ByteGNN analyzes the problems of existing distributed GNN training systems: higher network communication costs, lower CPU utilization, and GPUs that cannot bring significant training benefits. ByteGNN divides the minibatch of graph sampling into five basic operations and expresses the sampling process using a DAG composed of basic operations, which enables fine-grained parallelism within the sampling. ByteGNN designs a two-level scheduling strategy to adaptively adjust the resources allocated for sampling and training to maximize CPU utilization and speed up training. ByteGNN designs a partitioning method specific to minibatch graph sampling to reduce the large amount of network communication caused by graph sampling during training.